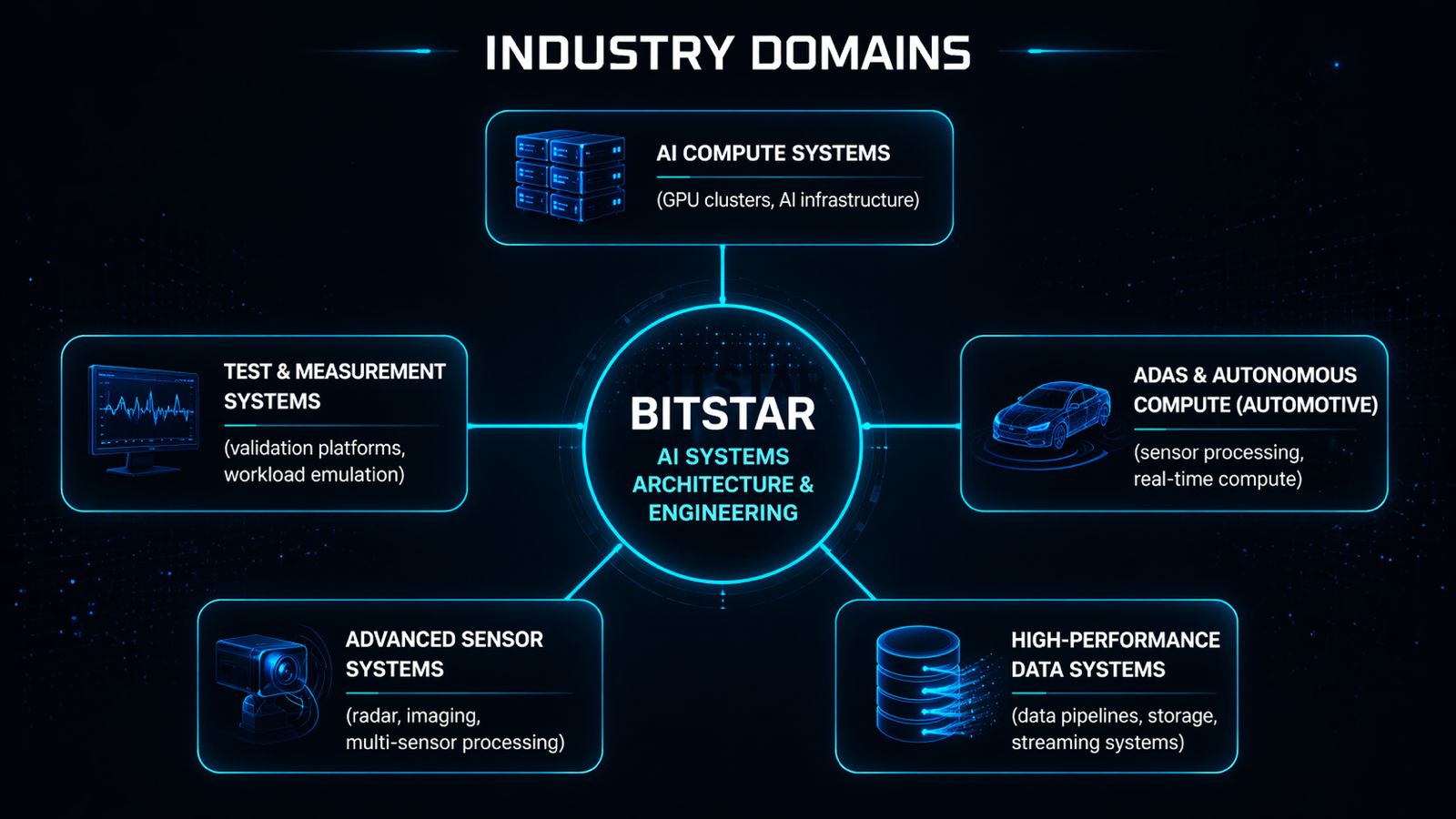

AI Infrastructure & HPC Systems

AI infrastructure is constrained by dataflow, not raw compute. As GPU clusters scale, data movement, storage coordination, and workload scheduling become the bottlenecks that cap utilization and raise cost.

- Data pipelines lag GPU demand

- Fabric contention adds latency

- I/O imbalance leaves GPUs idle

- Scaling multiplies control overhead

- Observability stays fragmented